(Baseado integralmente no arquivo: “Digital Isolator Design Guide” – Texas Instruments)

1 — Princípios de Funcionamento de Isoladores Digitais

A isolação galvânica é uma técnica essencial para sistemas eletrônicos modernos, permitindo que dois blocos de um circuito troquem sinais sem que exista continuidade elétrica entre eles. Essa separação impede que correntes contínuas ou transitórias de alta tensão atravessem para o outro lado, protegendo microcontroladores, ASICs, FPGAs e até o operador humano.

Nos isoladores digitais modernos, como mostrado no documento da Texas Instruments, a estrutura básica combina três elementos:

um transmissor (TX), um barreira isolante capacitiva de SiO₂ e um receptor (RX). O papel do transmissor é converter o sinal digital de entrada para uma forma compatível com a barreira; o receptor reconstrói o sinal digital do outro lado. A TI utiliza capacitores de dióxido de silício (SiO₂) como elemento isolante, oferecendo alta resistência dielétrica e confiabilidade a longo prazo.

Dois métodos principais são usados para transportar o sinal através dessa barreira: arquitetura baseada em bordas (edge-based) e arquitetura baseada em chaveamento liga/desliga (OOK – On-Off Keying).

1.1 Comunicação Baseada em Bordas (Edge-Based Communication)

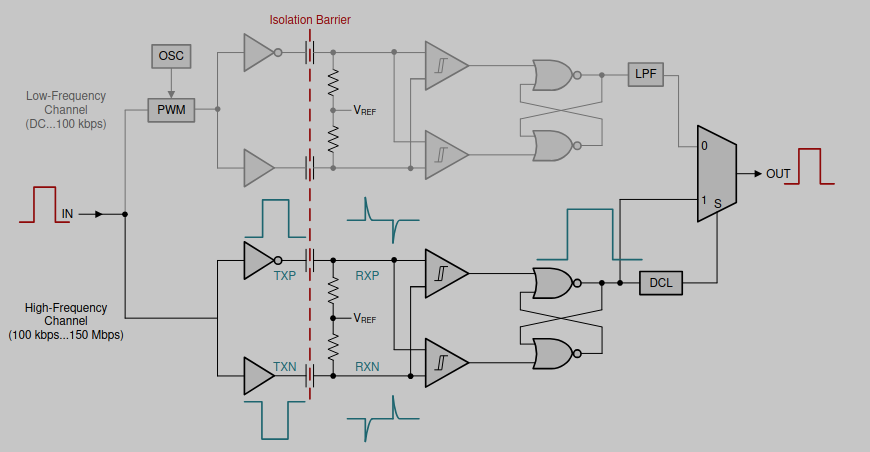

Nesta arquitetura — utilizada em famílias como ISO73xx, ISO74xx, ISO71xx, ISO76xx, ISO75xx e ISO72xx — o dispositivo possui dois canais internos:

• um canal de alta frequência (HF) que opera entre 100 kbps e 150 Mbps,

• e um canal de baixa frequência (LF) que cobre de 100 kbps até DC.

Quando um sinal entra no canal HF, ele é convertido para diferencial, passa por redes RC que transformam suas transições em pulsos estreitos e, em seguida, é processado por comparadores e um flip-flop digital. Já sinais de baixa frequência, que exigiriam capacitores internos muito grandes, são modulados em largura de pulso (PWM) usando um oscilador interno. Isso cria uma portadora de alta frequência capaz de atravessar a barreira capacitiva; na saída, um filtro passa-baixa remove a portadora, recuperando o dado original.

1.2 Comunicação Baseada em OOK (On-Off Keying)

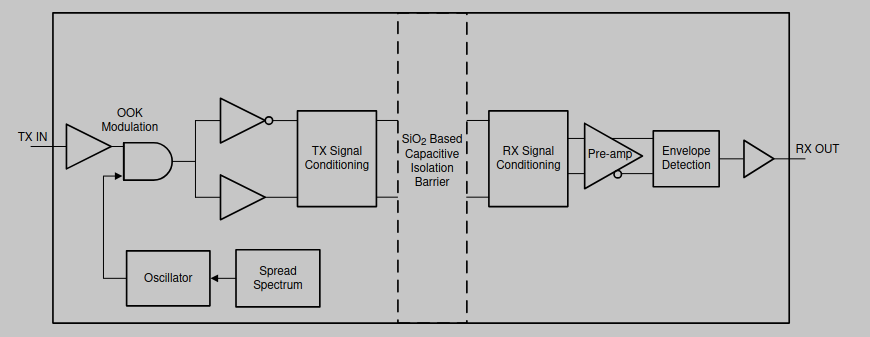

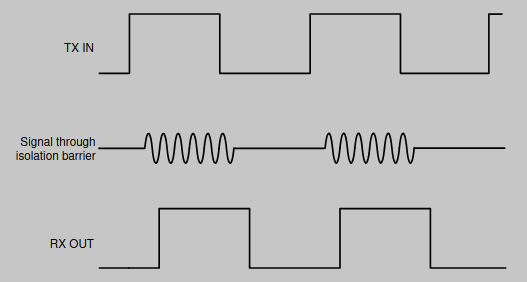

A segunda abordagem utiliza modulação OOK, presente nas famílias ISO67xx, ISO78xx e ISO77xx. Nesse método, um dos estados lógicos do sinal digital é representado pela presença de uma portadora de rádio-frequência interna, enquanto o outro estado é transmitido pela ausência dessa portadora.

O sinal modulado atravessa a barreira isolante e chega atenuado ao receptor. Do outro lado, um pré-amplificador aumenta o sinal, e um detector de envoltória (envelope detector) recupera a forma digital original. A arquitetura ainda utiliza condicionamento de sinal para melhorar a rejeição de modo comum, resultando em maior imunidade a transientes (CMTI).

2 — Aplicações Típicas de Isoladores Digitais

(Baseado integralmente no arquivo: “Digital Isolator Design Guide” – Texas Instruments)

Os isoladores digitais são amplamente utilizados em sistemas eletrônicos modernos para proteger circuitos sensíveis, permitir comunicação entre domínios de tensão diferentes e eliminar problemas de circulação de correntes de terra (ground loops). Como mostram os exemplos do documento, eles podem ser aplicados tanto em sinais digitais simples quanto em transceptores completos como RS-232, RS-485 e SPI.

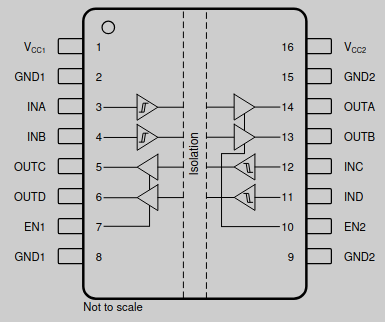

Antes de observar aplicações específicas, é útil entender a estrutura geral de um isolador digital. Um dispositivo típico possui dois domínios independentes, alimentados por VCC1/GND1 e VCC2/GND2, o que permite que cada lado opere em tensões diferentes e totalmente isoladas.

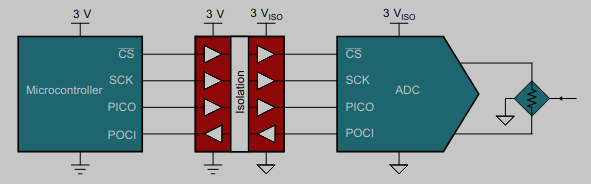

2.1 Isolação em Interfaces SPI

A aplicação mais simples envolve isolar um barramento SPI entre um microcontrolador e um conversor A/D ou A/D/D. Mesmo sendo um sistema de baixa tensão e single-ended, a isolação quebra laços de terra e protege contra picos vindos da seção de potência.

Isoladores das famílias ISO7x31 e ISO7x41, com 3 ou 4 canais, são comumente usados para isolar sinais SCK, MISO (POCI), MOSI (PICO) e CS. A isolação garante integridade do sinal mesmo diante de ruídos de modo comum.

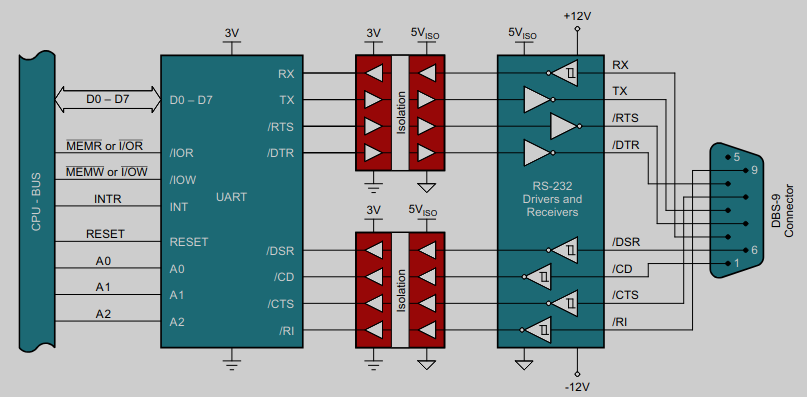

2.2 Isolação em Interfaces RS-232

A interface RS-232 exige vários sinais de controle além de RX e TX, o que demanda dois isoladores quádruplos para isolar completamente a comunicação entre o transceptor RS-232 e o UART interno do sistema. Mesmo que o sistema seja de baixa tensão, a fonte simétrica de ±12 V utilizada no barramento exige isolação devido aos riscos de transientes e diferenças de potencial.

A isolação também permite proteger o lado digital de microcontroladores caso o barramento RS-232 seja alimentado a partir de fontes mais altas, comuns em equipamentos industriais.

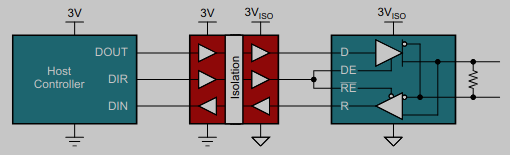

2.3 Isolação em Interfaces RS-485

O RS-485 opera de forma diferencial e é amplamente usado em redes industriais. Mesmo com toda a interface sendo de baixa tensão, isolar o lado de controle é necessário devido ao fato de que os nós da rede podem estar referenciados a potenciais de terra muito diferentes.

A isolação permite a comunicação mesmo quando há diferenças significativas de potencial entre diferentes trechos da rede.

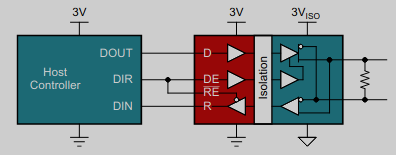

2.4 Funções Isoladas Integradas

Alguns dispositivos integram tanto o transceptor quanto o isolador em um único encapsulamento, reduzindo custo e quantidade de componentes na placa. Esse tipo de solução é mais simples e compacta, ideal para aplicações industriais e automação.

O exemplo fornecido no documento mostra um transceptor RS-485 com isolação integrada. Isso facilita o projeto e reduz riscos de erros de conexão entre isolador e transceptor separados.

3 — Guia de Seleção de Isoladores Digitais

Escolher o isolador digital adequado é uma etapa essencial no projeto de sistemas que exigem segurança elétrica, robustez contra ruídos e transmissão confiável de dados. O documento da Texas Instruments apresenta os principais parâmetros que devem ser analisados durante a seleção, bem como uma tabela comparativa das famílias de isoladores disponíveis.

3.1 Parâmetros Importantes na Escolha de um Isolador

Ao analisar um datasheet de isoladores digitais, alguns parâmetros são fundamentais para garantir desempenho e segurança no projeto:

1. Desempenho de isolação

O isolador deve suportar tensões elevadas entre seus domínios, e isso é especificado por:

- VIOTM — tensão máxima transitória de isolação (até 60 s).

- VISO — capacidade de suportar tensão de isolação aplicada.

- VIORM — tensão máxima repetitiva de pico.

- VIOWM — tensão de trabalho contínua entre os domínios.

- VIOSM — tensão de surto (impulso de 1,2 µs / 50 µs).

Esses valores determinam se o dispositivo é adequado para aplicações críticas como automação industrial, motores, veículos híbridos ou equipamentos médicos.

2. Parâmetros de temporização

Esses parâmetros afetam diretamente a integridade e o sincronismo dos sinais:

- Taxa de dados (Data Rate).

- Atraso de propagação (Propagation Delay).

- Desvio entre canais (Skew), importante para interfaces como SPI.

- Filtro de glitches, quando presente, aumenta o atraso mas melhora robustez contra ruído.

3. Imunidade a transientes de modo comum (CMTI)

O CMTI indica a capacidade do isolador de suportar variações rápidas de potencial entre os dois lados da barreira sem introduzir erros de comunicação. Quanto maior o CMTI, maior a robustez do sistema.

4. Consumo de energia

Essencial para sistemas alimentados por baterias ou que utilizam muitos canais de isolação. O consumo varia conforme a família e a taxa de dados.

5. Encapsulamento

Importante para requisitos normativos de isolação:

- Creepage: distância física mínima sobre a superfície entre os lados isolados.

- Clearance: distância pelo ar entre os terminais.

- CTI (Comparative Tracking Index): indica resistência do encapsulamento a degradação superficial em tensão; valores maiores permitem encapsulamentos menores para a mesma tensão de trabalho.

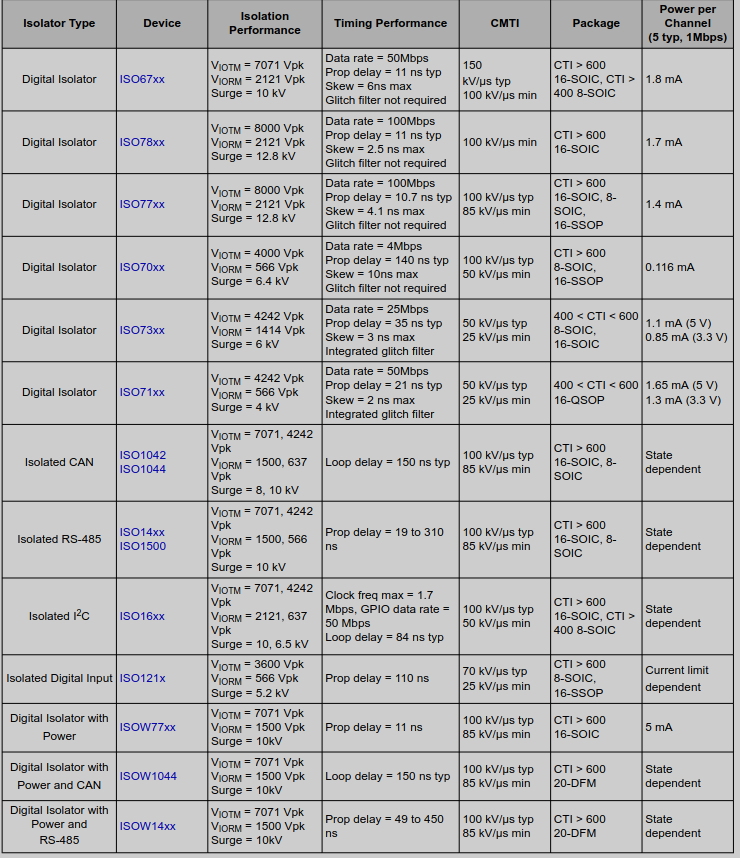

3.2 Famílias de Isoladores Digitais

O documento reúne uma tabela extensa listando as principais famílias de isoladores da Texas Instruments, incluindo isoladores simples, isoladores com transceptores integrados (CAN, RS-485, I²C) e isoladores que incorporam fonte de alimentação isolada.

Essa tabela permite rápida comparação entre tensões suportadas, consumo, CMTI, desempenho de temporização e encapsulamentos disponíveis.

A tabela apresenta famílias como:

- ISO67xx — alta isolação, 50 Mbps, CMTI típico de 150 kV/µs.

- ISO78xx — isolação reforçada até 8000 Vpk, até 100 Mbps.

- ISO77xx — desempenho elevado com baixíssimo consumo.

- ISO70xx, ISO73xx, ISO71xx — opções com diferentes níveis de isolação e taxas de dados.

- ISOW — isoladores com alimentação integrada.

- ISO1042, ISO14xx, ISO121x — isoladores com funções CAN, RS-485 e entradas digitais isoladas.

Essa tabela funciona como uma referência direta para selecionar rapidamente a família correta conforme o tipo de aplicação, taxa de dados, consumo e exigências de isolação elétrica.

4 — Diretrizes de Projeto de PCB para Isoladores Digitais

O desempenho de um isolador digital depende não apenas do componente em si, mas também da qualidade do projeto de PCB. Um layout inadequado pode gerar ruídos, perda de integridade de sinal, aumento de EMI e redução da isolação efetiva. Por isso, o guia da Texas Instruments fornece recomendações fundamentais para garantir uma placa confiável, mesmo em aplicações de alta velocidade ou alta tensão.

4.1 Material da PCB

Para circuitos digitais abaixo de 150 Mbps e trilhas de até 10 polegadas, recomenda-se usar FR-4, material que atende UL94-V0 e apresenta:

- Baixas perdas dielétricas em alta frequência

- Baixa absorção de umidade

- Boa rigidez mecânica

- Comportamento autoextinguível

Esse material é o mais adequado para aplicações envolvendo isoladores digitais.

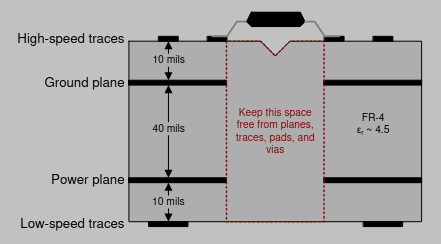

4.2 Empilhamento de Camadas (Layer Stack)

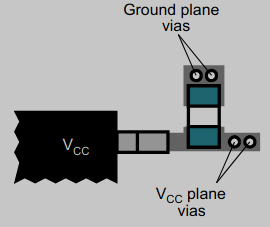

O documento recomenda um PCB com mínimo de quatro camadas, na ordem:

- Camada superior — trilhas de alta velocidade

- Plano de terra

- Plano de alimentação

- Camada inferior — trilhas de baixa velocidade

Esse empilhamento reduz EMI, fornece retorno de corrente de baixa indutância e cria capacitância distribuída entre os planos de energia e terra.

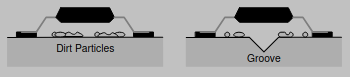

4.3 Distância de Escoamento (Creepage Distance)

Creepage é o caminho ao longo da superfície do material entre dois pontos condutivos. Para isolação adequada, esse caminho deve ser longo o bastante para evitar formação de trilhas condutivas por poeira, umidade ou poluentes ambientais.

O guia recomenda:

- Usar encapsulamentos de isoladores que possuam creepage adequado

- Manter todas as camadas da PCB sem trilhas abaixo do isolador

- Utilizar cavidades (grooves) para aumentar a distância efetiva quando necessário

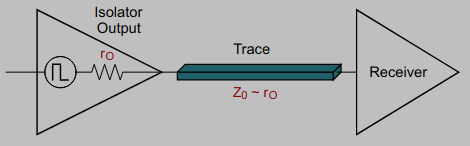

4.4 Linhas de Transmissão com Impedância Controlada

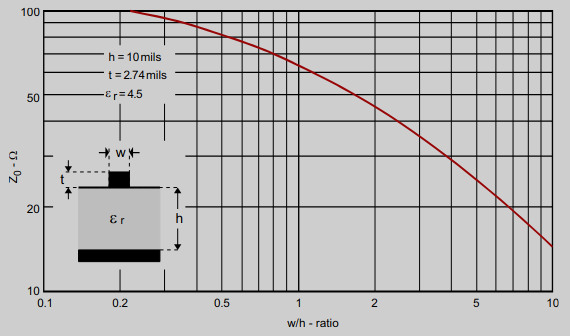

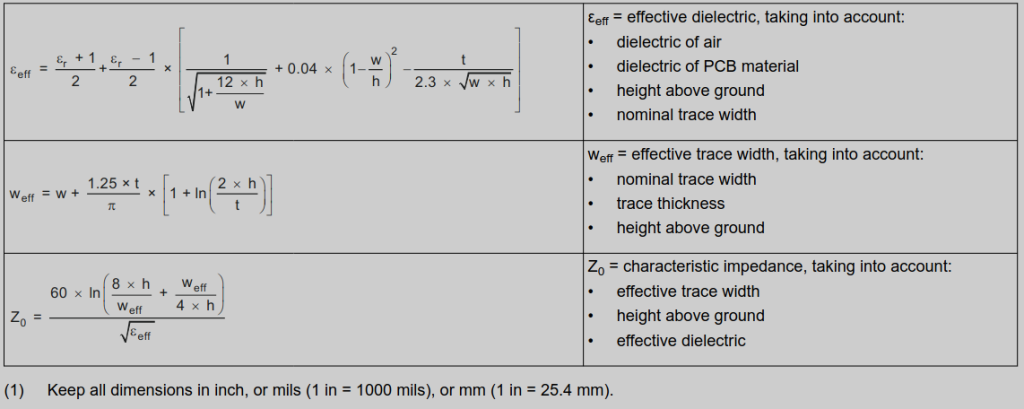

Quando trilhas transportam sinais rápidos, a impedância característica deve ser compatível com a impedância de saída do isolador, conceito chamado source-impedance matching.

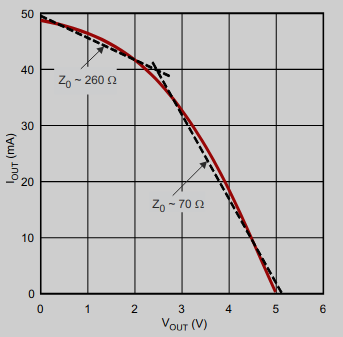

A impedância de saída típica de um isolador varia conforme a região da curva Vout × Iout. No exemplo do documento, o valor aproximado é:

- 260 Ω em baixas tensões

- 70 Ω na região de comutação

Por isso, as trilhas devem ser dimensionadas para se aproximarem de 70 Ω, garantindo baixa reflexão e menor EMI.

O documento também apresenta a relação entre largura da trilha (w), altura até o plano de terra (h) e impedância Z₀.

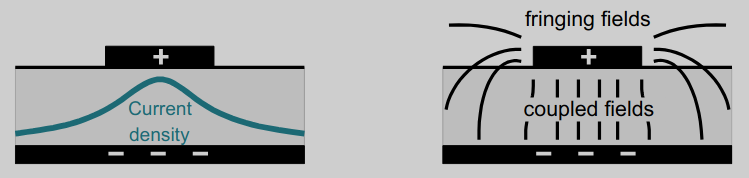

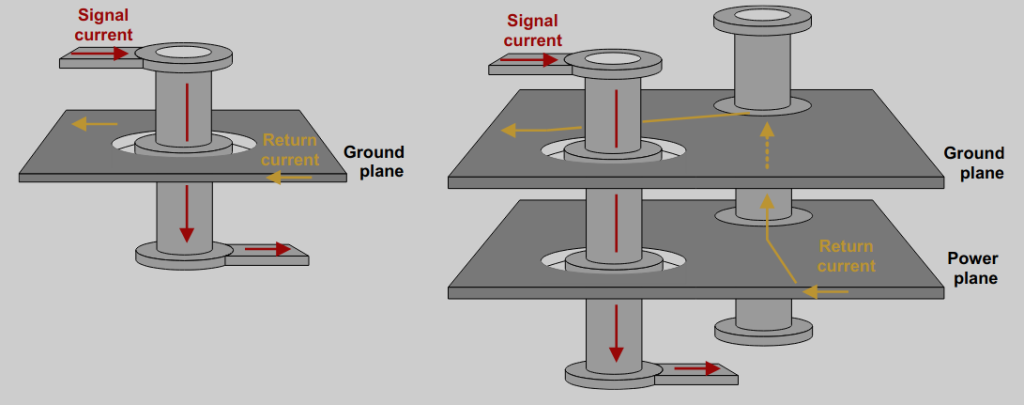

4.5 Planos de Referência (Reference Planes)

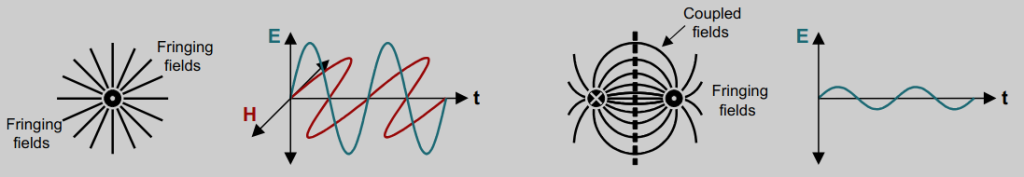

Planos de terra e alimentação devem ser sólidos, contínuos e livres de recortes. Eles cumprem diversas funções:

- Estabelecem o retorno de corrente de baixa indutância

- Reduzem emissão eletromagnética

- Criam forte acoplamento elétrico com trilhas de alta velocidade

O guia mostra que quando o sinal corre em um plano e o retorno está imediatamente abaixo, os campos elétrico e magnético se cancelam, reduzindo EMI.

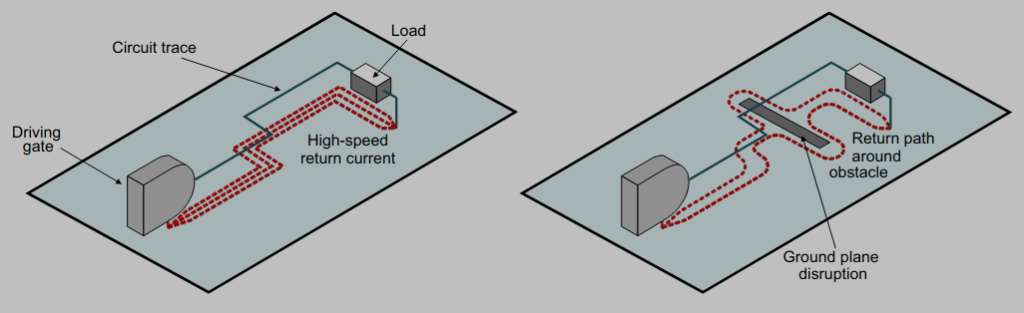

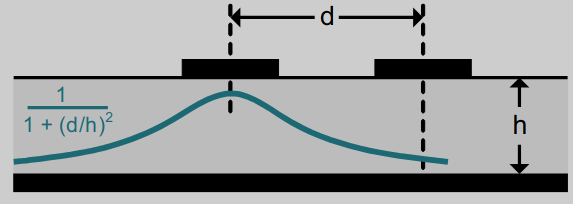

4.6 Roteamento de Trilhas (Routing Guidelines)

Recomendações principais:

- Separação de trilhas: manter distância de ≥ 3 × altura até o plano de terra para minimizar crosstalk.

- Evitar ângulos de 90°: usar curvas de 45° para impedir mudanças bruscas na impedância.

- Evitar buracos ou fendas no plano de terra que desviem o retorno de corrente e aumentem EMI.

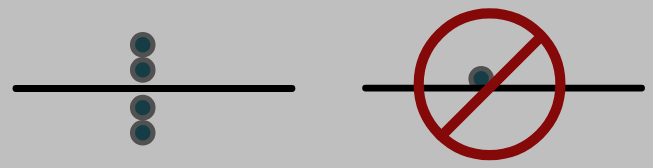

- Evitar passar trilhas por clareiras de vias.

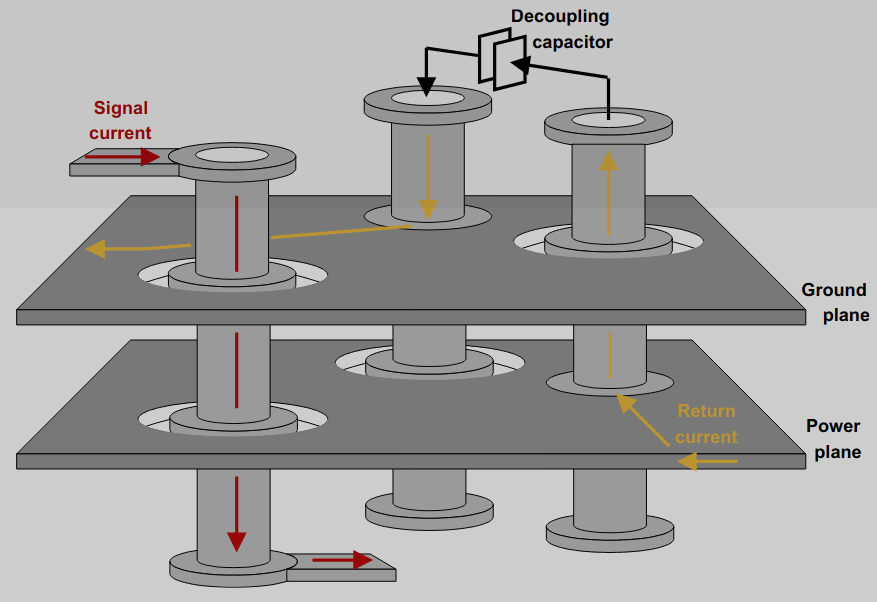

- Minimizar troca de camadas: cada mudança de camada adiciona indutância e pode exigir vias de retorno.

- Evitar mudanças entre planos de referência diferentes (ex.: terra → alimentação), pois isso exige vias adicionais e capacitores de desacoplamento.

4.7 Vias

Vias possuem capacitância e indutância parasitas, afetando o comportamento de alta frequência. O guia recomenda:

- Usar vias pequenas para sinais

- Usar vias múltiplas em paralelo para reduzir indutância

- Conectar capacitores ao plano de terra ou alimentação com duas vias por terminal

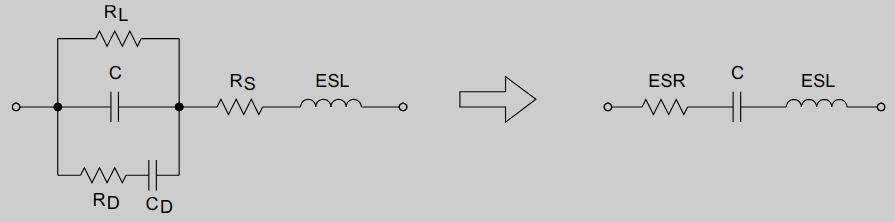

4.8 Capacitores de Desacoplamento

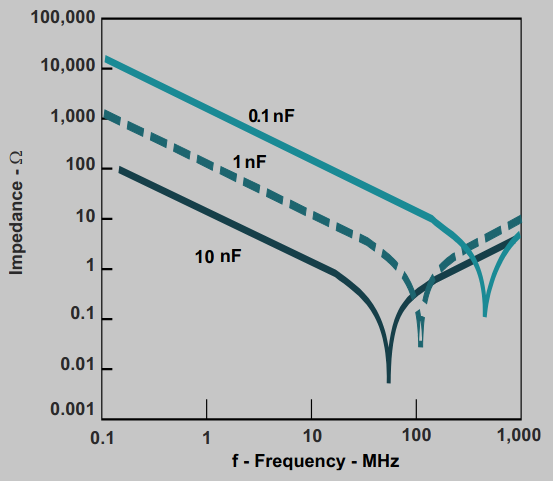

Capacitores de desacoplamento evitam que oscilações internas dos circuitos digitais provoquem quedas na alimentação. No documento:

- Capacitores são modelados como um circuito série RLC

- A impedância é mínima na frequência de ressonância (SRF)

- O uso de vários capacitores em paralelo reduz tanto impedância capacitiva quanto indutiva

O guia recomenda:

- 1 µF a 10 µF perto dos reguladores e entrada da placa

- 0,1 µF ou 0,01 µF muito próximos de cada CI de alta velocidade

Resumo

O guia de projeto apresentado fornece aos desenvolvedores de sistemas galvanicamente isolados um conjunto completo de fundamentos para iniciar o uso dos isoladores digitais da Texas Instruments no menor tempo possível. Esse material explica de forma direta os princípios de operação dos isoladores, mostra como posicioná-los corretamente em um sistema eletrônico e apresenta recomendações essenciais para o desenvolvimento de placas de circuito compatíveis com requisitos de EMC (compatibilidade eletromagnética).

Mesmo diante da grande quantidade de literatura técnica e cursos sobre layout de PCB, o documento reúne diretrizes claras e coerentes que permitem alcançar um design mais sólido e com menor emissão eletromagnética. Ao seguir as recomendações apresentadas, o projetista pode obter um desempenho superior e confiável no uso de isoladores digitais, reduzindo riscos de falhas e otimizando o processo de desenvolvimento.

O documento também reforça que o uso apropriado de isoladores digitais não se limita apenas a proteção contra altas tensões, mas inclui aspectos críticos como imunidade a transientes, integridade de sinal, boas práticas de roteamento e o papel essencial de um empilhamento adequado de camadas. Dessa forma, o projetista pode alcançar maior robustez e confiabilidade no sistema final.

6 — Referências

O documento lista as seguintes referências utilizadas para embasar as definições, metodologias e recomendações técnicas:

- Texas Instruments – Pushing the envelope with high-performance, digital-isolation technology (Analog Applications Journal).

- Texas Instruments – Enabling high voltage signal isolation quality and reliability (White Paper).

- Texas Instruments – High-voltage reinforced isolation: Definitions and test methodologies (Marketing White Paper).

- Johnson / Graham, 1993 – High-speed Digital Design.

- Ott, 1988 – Noise Reduction Techniques in Electronic Systems.

- Archambeault, 2001 – Eliminating the myths about printed circuit board power/ground plane decoupling.

Sobre o Autor

Carlos Delfino

administrator

Um Eterno Aprendiz.

Professor de Introdução a Programação, programação com JavaScript, TypeScript, C/C++ e Python

Professor de Eletrônica Básica

Professor de programação de Microcontroladores.

Embarcatecher