## **Applications Note: SY5810** Single Stage Flyback And PFC Controller With Primary Side Control For LED Lighting *Preliminary datasheet*

## **General Description**

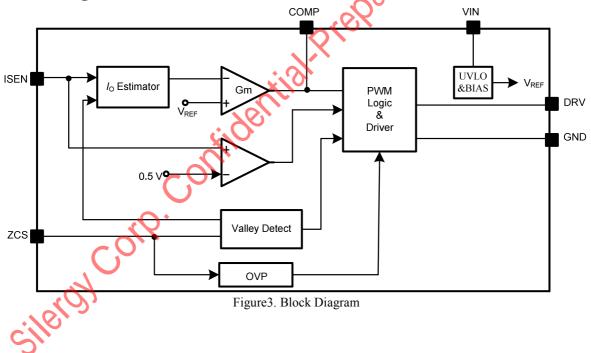

The SY5810 is a single stage Flyback and PFC controller targeting at LED lighting applications. It is a primary side controller without applying any secondary feedback circuit for low cost, and drives the Flyback converter in the quasi-resonant mode to achieve higher efficiency. It keeps the Flyback converter in constant on time operation to achieve high power factor.

# **Ordering Information**

Temperature Range: -40°C to 85°C

| Ordering Number | Package type | Note |

|-----------------|--------------|------|

| SY5810ABC       | SOT23-6      |      |

## Features

- Primary side control eliminates the opto-coupler.

- Valley turn-on of the primary MOSFET to achieve low switching losses

- 0.3V primary current sense reference voltage leads to a lower sense resistance thus a lower conduction loss.

- Internal high current MOSFET driver: 0.25A sourcing and 0.5A sinking

- Low start up current: 15µA typical

- Reliable short LED and Open LED protection

- Power factor >0.90 with single-stage conversion.

- Compact package: SOT23-6

# Applications

- LED lighting

- Down light

- Tube lamp

- PAR lamp Bulb **Typical Applications** T1 1.6mH n=4.3 D2 Output R3 C3 20V/200mA R2 **≥** NS 100K 440u**∇**ル 100K 4 7n 0 C1 R1 M 100n 1MAC input 90~264V D1 0 RT1 D3R1/10 ع C4 10u R5 sileroy 100K **R9/10** 🗄 Q1 ISEN DRY w GND VI R6 R10 COMP ZC 15K 10K R7 SY5810 500 **≩**R11/1

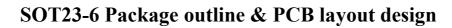

- Figure 1. Schematic Diagram SOT23-6

-C5 2μ

Top Mark: GZxyz for SY5810ABC(device code: GZ, x=year code, y=week code, z= lot number code)

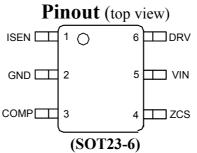

| Pin Name                  | SOT23-6 | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|---------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| ISEN                      | 1       | Current sense pin. Connect this pin to the source of the primary switch.<br>Connect the sense resistor across the source of the primary switch and the GND pin.<br>(current sense resister R <sub>S</sub> : $R_s = k \frac{V_{REF} \cdot N_{PS}}{I_{OUT}}$ , $k = 0.167$ )                                                                                                                                                                                                 |  |  |  |

| GND                       | 2       | Ground pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| COMP                      | 3       | Loop compensation pin. Connect a RC network across this pin and ground to stabilize the control loop.                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| ZCS                       | 4       | Inductor current zero-crossing detection pin. This pin receives the auxiliary winding voltage by a resister divider and detects the inductor current zero crossing point. This pin also provides over voltage protection and line regulation modification function simultaneously. If the voltage on this pin is above $V_{ZCS,OVP}$ the IC would enter over voltage protection mode. Good line regulation can be achieved by adjusting the upper resistor of the divider. |  |  |  |

| VIN                       | 5       | Power supply pin. This pin also provides output over voltage protection along with ZCS pin.                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| DRV                       | 6       | Gate driver pine Connect this pin to the gate of primary MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| vin 5 along with ZCS pin. |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

AN\_SY5810 Rev. 0.1A Silergy Corp. Confidential- Prepared for Customer Use Only

2

# Absolute Maximum Ratings (Note 1)

| $\boldsymbol{\Theta}$                  |                       |

|----------------------------------------|-----------------------|

| VIN, DRV                               |                       |

| Supply Current I <sub>VIN</sub>        | 30mA                  |

| ZCS                                    | V <sub>IN</sub> +0.3V |

| ISEN, COMP                             |                       |

| Power Dissipation, @ TA = 25°C SOT23-6 | 0.6W                  |

| Package Thermal Resistance (Note 2)    |                       |

| SOT23-6, θ JA                          | 170°C/W               |

| SOT23-6, θ JC                          | 130°C/W               |

| Temperature Range                      |                       |

| Lead Temperature (Soldering, 10 sec.)  |                       |

| Storage Temperature Range              |                       |

| Storage remperature range              | 05 0 10 150 0         |

# **Recommended Operating Conditions** (Note 3)

| VIN. DRV                   | <br>8V~154V       |

|----------------------------|-------------------|

|                            | 01 15.11          |

| Junction Temperature Range | <br>40°C to 125°C |

|                            | 1000 10500        |

| Ambient Temperature Range  | <br>40°C to 105°C |

|                            |                   |

# **Block Diagram**

# **Electrical Characteristics**

$(V_{IN} = 12V \text{ (Note 3)}, T_A = 25^{\circ}C \text{ unless otherwise specified)}$

|                                  |                       | vise specifica)                        | 1          |                           |       |      |

|----------------------------------|-----------------------|----------------------------------------|------------|---------------------------|-------|------|

| Parameter                        | Symbol                | Test Conditions                        | Min        | Тур                       | Max   | Unit |

| Power Supply Section             |                       |                                        |            |                           |       |      |

| Input voltage range              | V <sub>VIN</sub>      |                                        | 8          |                           | 15.4  | V    |

| VIN turn-on threshold            | V <sub>VIN,ON</sub>   |                                        |            |                           | 17.6  | V    |

| VIN turn-off threshold           | V <sub>VIN,OFF</sub>  |                                        | 6.0        |                           | 7.9   | V    |

| VIN OVP voltage                  | V <sub>VIN,OVP</sub>  |                                        |            | V <sub>VIN,ON</sub> +0.85 |       | V    |

| Start up Current                 | I <sub>ST</sub>       | $V_{VIN} < V_{VIN,OFF}$                |            | 15                        |       | μA   |

| Operating Current                | I <sub>VIN</sub>      | C <sub>L</sub> =100pF,f=15kHz          |            | 1                         |       | mA   |

| Shunt current in OVP mode        | I <sub>VIN,OVP</sub>  | V <sub>VIN</sub> >V <sub>VIN,OVP</sub> | 1.6        | 2                         | 2.5   | mA   |

| Error Amplifier Section          |                       |                                        |            |                           |       |      |

| Internal reference voltage       | $V_{REF}$             |                                        | 0.294      | 0.3                       | 0.306 | V    |

| Current Sense Section            |                       |                                        |            |                           |       |      |

| Current limit reference voltage  | V <sub>ISEN,MAX</sub> |                                        |            | 0.5                       |       | V    |

| ZCS pin Section                  |                       |                                        | . (        |                           |       |      |

| ZCS pin OVP voltage<br>threshold | V <sub>ZCS,OVP</sub>  |                                        | $\sum_{i}$ | 1.42                      |       | V    |

| Gate Driver Section              |                       | ام ا                                   | 2          |                           |       |      |

| Gate driver voltage              | V <sub>Gate</sub>     |                                        |            | V <sub>VIN</sub>          |       | V    |

| Maximum source current           | I <sub>SOURCE</sub>   | 00                                     |            | 0.25                      |       | А    |

| Minimum sink current             | I <sub>SINK</sub>     | XQX                                    |            | 0.5                       |       | А    |

| Max ON Time                      | T <sub>ON,MAX</sub>   | $V_{COMP} = 1.5V$                      |            | 24                        |       | μs   |

| Min ON Time                      | T <sub>ON,MIN</sub>   |                                        |            | 400                       |       | ns   |

| Max OFF Time                     | T <sub>OFF,MAX</sub>  |                                        |            | 39                        |       | μs   |

| Min OFF Time                     | T <sub>OFF,MIN</sub>  | ×                                      |            | 2                         |       | μs   |

| Maximum switching frequency      | $f_{MAX}$             |                                        |            | 120                       |       | kHz  |

| Thermal Section                  |                       | 76,                                    |            |                           |       |      |

| Thermal Shutdown<br>Temperature  | T <sub>SD</sub>       | 2                                      |            | 150                       |       | С    |

**Note 1**: Stresses beyond the "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**Note 2**:  $\Theta_{JA}$  is measured in the natural convection at  $T_A = 25^{\circ}$ C on a low effective single layer thermal conductivity test board of JEDEC 51-3 thermal measurement standard. Test condition: Device mounted on 2" x 2" FR-4 substrate PCB, 2oz copper, with minimum recommended pad on top layer and thermal vias to bottom layer ground plane.

Note 3 Uncrease VIN pin voltage gradually higher than  $V_{VIN,ON}$  voltage then turn down to 12V.

## Operation

SY5810 is a constant current Flyback controller with primary side control and PFC function that targets at LED lighting applications.

The Device provides primary side control to eliminate the opto-couplers or the secondary feedback circuits, which would cut down the cost of the system.

High power factor is achieved by constant on operation mode, with which the control scheme and the circuit structure are both simple.

In order to reduce the switching losses and improve EMI performance, Quasi-Resonant switching mode is applied, which means to turn on the power MOSFET at voltage valley; the start up current of SY5810 is rather small (15uA typically) to reduce the standby power loss further; the maximum switching frequency is clamped to 120kHz to reduce switching losses and improve EMI performance when the converter is operated at light load condition.

SY5810 provides reliable protections such as Short Circuit Protection (SCP), Open LED Protection (OLP), Over Temperature Protection (OTP), etc.

SY5810 is available with STO23-6

# Applications Information

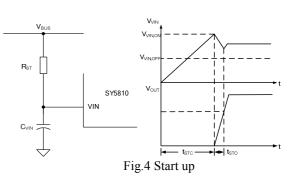

### <u>Start up</u>

After AC supply or DC BUS is powered on, the capacitor  $C_{VIN}$  across VIN and GND pin-is charged up by BUS voltage through a start up resistor  $R_{ST}$ . Once  $V_{VIN}$  rises up to  $V_{VIN-ON}$ , the internal blocks start to work.  $V_{VIN}$  will be pulled down by internal consumption of IC until the auxiliary winding of Flyback transformer could supply enough energy to maintain  $V_{VIN}$  above  $V_{VIN-OFF}$ .

The whole start up procedure is divided into two sections shown in Fig.4.  $t_{STC}$  is the  $C_{VIN}$  charged up section, and  $t_{STO}$  is the output voltage built-up section. The start up time  $t_{ST}$  composes of  $t_{STC}$  and  $t_{STO}$ , and usually  $t_{STO}$  is much smaller than  $t_{STC}$ .

The start up resistor  $R_{ST}$  and  $C_{VIN}$  are designed by rules below:

(a) Preset start-up resistor  $R_{ST}$ , make sure that the current through  $R_{ST}$  is larger than  $I_{ST}$  and smaller than  $I_{VIN\_OVP}$

$$\frac{V_{BUS}}{I_{VIN_{OVP}}} < R_{ST} < \frac{V_{BUS}}{I_{ST}} (1)$$

Where V\_{BUS} is the BUS line voltage.

(b) Select  $C_{VIN}$  to obtain an ideal start up time  $t_{ST}$ , and ensure the output voltage is built up at one time.

$$C_{\rm VIN} = \frac{\left(\frac{V_{\rm BUS}}{R_{\rm ST}} - I_{\rm ST}\right) \times t_{\rm ST}}{V_{\rm VIN_ON}} (2)$$

(d) If the  $C_{VIN}$  is not big enough to build up the output voltage at one time. Increase  $C_{VIN}$  and decrease  $R_{ST}$ , go back to step (a) and redo such design flow until the ideal start up procedure is obtained.

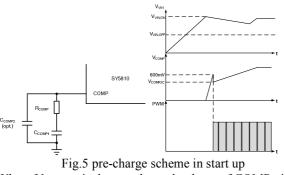

#### Internal pre-charge design for quick start up

After  $V_{VIN}$  exceeds  $V_{VIN,ON}$ ,  $V_{COMP}$  is pre-charged by an internal current source. The PWM block won't start to output PWM signals until  $V_{COMP}$  is over the initial voltage  $V_{COMP,IC}$ , which can be programmed by  $R_{COMP}$ . Such design is meant to reduce the start up time shown in Fig.5.

The voltage pre-charged  $V_{COMP\_IC}$  in start-up procedure can be programmed by  $R_{COMP}$

$$V_{\text{COMP IC}} = 600 \text{mV} - 300 \mu \text{A} \times R_{\text{COMP}} (3)$$

## **SY5810**

Where  $V_{COMP-IC}$  is the pre-charged voltage of COMP pin.

Generally, a big capacitance of  $C_{COMP}$  is necessary to achieve high power factor and stabilize the system loop (1 $\mu$ F~2 $\mu$ F recommended); The voltage pre-charged in start-up procedure can be programmed by R<sub>COMP</sub>; On the other hand, larger R<sub>COMP</sub> can provide larger phase margin for the control loop; A small ceramic capacitor is added to suppress high frequency interruption (10pF~100pF is recommended if necessary)

#### Shut down

After AC supply or DC BUS is powered off, the energy stored in the BUS capacitor will be discharged. When the auxiliary winding of Flyback transformer can not supply enough energy to VIN pin,  $V_{VIN}$  will drop down. Once  $V_{VIN}$  is below  $V_{VIN-OFF}$ , the IC will stop working and  $V_{COMP}$  will be discharged to zero.

#### Primary-side constant-current control

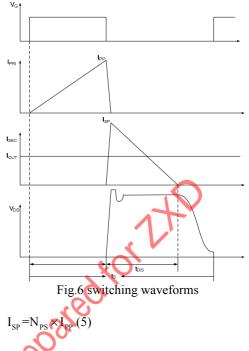

Primary side control is applied to eliminate secondary feedback circuit or opto-coupler, which reduces the circuit cost. The switching waveforms are shown in Fig.6.

The output current I<sub>OUT</sub> can be represented by,

$I_{OUT} = \frac{I_{SP}}{2} \times \frac{t_{DIS}}{t_s} (4)$

Where  $I_{SP}$  is the peak current of the secondary side;  $t_{DIS}$  is the discharge time of Flyback transformer;  $t_S$  is the switching period.

The secondary peak current is related with primary peak current, if the effect of the leakage inductor is neglected.

Where  $N_{PS}$  is the turns ratio of primary to secondary of the Flyback transformer.

Thus, I<sub>OUT</sub> can be represented by

$$I_{OUT} = \frac{N_{PS} \times I_{PP}}{2} \times \frac{t_{DIS}}{t_s} (6)$$

The primary peak current  $I_{PP}$  and inductor current discharge time  $t_{DIS}$  can be detected by the IC, and the effect of the leakage inductor can be compensated by internal control scheme.  $I_{OUT}$  can be induced finally by

$$I_{OUT} = \frac{k_1 \times k_2 \times V_{REF} \times N_{PS}}{R_s} (7)$$

Where  $k_1$  is the output current weight coefficient;  $k_2$  is the output modification coefficient;  $V_{REF}$  is the internal reference voltage;  $R_S$  is the current sense resistor.

$k_{1,}k_{2}$  and  $V_{REF}$  are all internal constant parameters,  $I_{OUT}$  can be programmed by  $N_{PS}$  and  $R_{S}.$

$$R_{S} = \frac{k_{1} \times k_{2} \times V_{REF} \times N_{PS}}{I_{OUT}} (8)$$

# <u>SY5810</u>

# <u>SY5810</u>

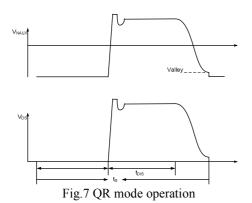

#### **Quasi-Resonant Operation**

QR mode operation provides low turn-on switching losses for Flyback converter.

The voltage across drain and source of the primary MOSFET is reflected by the auxiliary winding of the Flyback transformer. ZCS pin detects the voltage across the auxiliary winding by a resistor divider. When the voltage across drain and source of the primary MOSFET is at voltage valley, the MOSFET would be turned on.

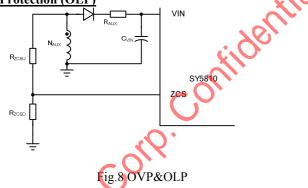

Over Voltage Protection (OVP) & Open LED Protection (OLP)

The output voltage is reflected by the auxiliary winding voltage of the Flyback transformer, and both ZCS pin and VIN pin provide over voltage protection function. When the load is null or large transient happens, the output voltage will exceed the rated value. When  $V_{VIN}$  exceeds  $V_{VIN,OVP}$  or  $V_{ZCS}$  exceeds  $V_{ZCS,OVP}$ , the over voltage protection is triggered and the IC will discharge  $V_{VIN}$  by an internal current source  $I_{VIN,OVP}$ . Once  $V_{VIN}$  is below  $V_{VIN,OFF}$ , the IC will shut down and be charged again by BUS voltage through start up resistor. If the over voltage

condition still exists, the system will operate in hiccup mode.

Thus, the turns of the auxiliary winding  $N_{AUX}$  and the resistor divider is related with the OVP function.

$$\frac{V_{ZCS\_OVP}}{V_{OVP}} = \frac{N_{AUX}}{N_S} \times \frac{R_{ZCSD}}{R_{ZCSU} + R_{ZCSD}} (9)$$

$$\frac{V_{VIN\_OVP}}{V_{OVP}} \ge \frac{N_{AUX}}{N_S} (10)$$

Where  $V_{OVP}$  is the output over voltage specification;  $R_{ZCSU}$  and  $R_{ZCSD}$  compose the resistor divider. The turns ratio of N<sub>s</sub> to N<sub>AUX</sub> and the ratio of R<sub>ZCSU</sub> to R<sub>ZCSD</sub> could be induced from equation (9) and (10).

## Short Circuit Protection (SCP)

When the output is shorted to ground, the output voltage is clamped to zero. The voltage of the auxiliary winding is proportional to the output winding, so  $V_{VIN}$  will drop down without auxiliary winding supply. Once  $V_{VIN}$  is below  $V_{VIN,OFF}$ , the IC will shut down and be charged again by the BUS voltage through the start up resistor. If the short circuit condition still exists, the system will operate in hiccup mode.

In order to guarantee SCP function not effected by voltage spike of auxiliary winding, a filter resistor  $R_{AUX}$  is needed (10 $\Omega$  typically) shown in Fig.8.

### Line regulation modification

The IC provides line regulation modification function to improve line regulation performance.

Due to the sample delay of ISEN pin and other internal delay, the output current increases with increasing input BUS line voltage. A small compensation voltage  $\Delta V_{ISEN-C}$  is added to ISEN pin during ON time to improve such performance. This  $\Delta V_{ISEN-C}$  is adjusted by the upper resistor of the divider connected to ZCS pin.

$$\Delta V_{\text{ISEN,C}} = V_{\text{BUS}} \times \frac{N_{\text{AUX}}}{N_{\text{P}}} \times \frac{1}{R_{\text{ZCSU}}} \times k_{3} (11)$$

Where  $R_{ZCSU}$  is the upper resistor of the divider; k3 is an internal constant as the modification coefficient;  $N_{AUX}$

7

## <u>SY5810</u>

and  $N_{\text{P}}$  are the turns of auxiliary winding and primary winding of the transformer.

The compensation is mainly related with  $R_{ZCSU},$  larger compensation is achieved with smaller  $R_{ZCSU}.$  Normally,  $R_{ZCS}$  ranges from 100k $\Omega{\sim}1M\Omega.$

Then R<sub>ZCSD</sub> can be selected by,

$$\frac{\frac{V_{ZCS\_OVP}}{V_{OUT}} \times \frac{N_{s}}{N_{AUX}}}{1 - \frac{V_{ZCS\_OVP}}{V_{OUT}} \times \frac{N_{s}}{N_{AUX}}} \times R_{ZCSU} > R_{ZCSD} (12),$$

And,

$$R_{ZCSD} \ge \frac{\frac{V_{ZCS_OVP}}{V_{OVP}} \times \frac{N_s}{N_{AUX}}}{1 - \frac{V_{ZCS_OVP}}{V_{OVP}} \times \frac{N_s}{N_{AUX}}} \times R_{ZCSU} (13)$$

Where  $V_{\rm OVP}$  is the output over voltage protection specification;  $V_{\rm OUT}$  is the rated output voltage;  $R_{\rm ZCSU}$  is the upper resistor of the divider;  $N_{\rm S}$  and  $N_{\rm AUX}$  are the turns of secondary winding and auxiliary winding separately.

## **Power Device Design**

#### **MOSFET and Diode**

When the operation condition is with maximum input voltage and full load, the voltage stress of MOSFET and secondary power diode is maximized;

$$V_{\text{MOS}_{DS}_{MAX}} = \sqrt{2} V_{\text{AC}_{MAX}} + N_{\text{PS}} \times (V_{\text{OUT}} + V_{\text{D}_{F}}) + \Delta V_{\text{S}} (14)$$

$$V_{\text{D}_{R}_{MAX}} = \frac{\sqrt{2} V_{\text{AC}_{MAX}}}{N_{\text{PS}}} + V_{\text{OUT}} (15)$$

Where  $V_{AC,MAX}$  is maximum input AC RMS voltage;  $N_{PS}$  is the turns ratio of the Flyback transformer;  $V_{OUT}$  is the rated output voltage;  $V_{D,F}$  is the forward voltage of secondary power diode;  $\Delta V_S$  is the overshoot voltage clamped by RCD snubber during OFF time.

When the operation condition is with minimum input voltage and full load, the current stress of MOSFET and power diode is maximized.

$$I_{MOS_{PK_{MAX}}} = I_{P_{PK_{MAX}}} (16)$$

$$I_{MOS_{RMS_{MAX}}} = I_{P_{RMS_{MAX}}} (17)$$

$$I_{D_{PK_{MAX}}} = N_{PS} \times I_{P_{PK_{MAX}}} (18)$$

$$I_{D_{AVG}} = I_{OUT} (19)$$

Where  $I_{P-PK-MAX}$  and  $I_{P-RMS-MAX}$  are maximum primary peak current and RMS current, which will be introduced later.

## Transformer (N<sub>PS</sub> and L<sub>M</sub>)

$N_{PS}$  is limited by the electrical stress of the power MOSFET:

$$N_{PS} \leq \frac{V_{MOS\_(BR)DS} \times 90\% \cdot \sqrt{2} V_{AC\_MAX} \cdot \Delta V_{S}}{V_{OUT} + V_{D\_F}}$$

(20)

Where  $V_{MOS,(BR)DS}$  is the breakdown voltage of the power MOSPET.

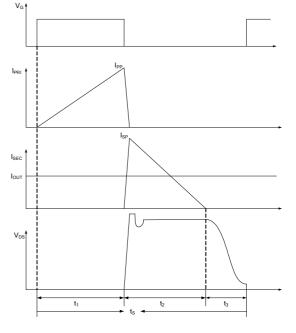

In Quasi-Resonant mode, each switching period cycle  $t_s$  consists of three parts: current rising time  $t_1$ , current falling time  $t_2$  and quasi-resonant time  $t_3$  shown in Fig.9.

Fig.9 switching waveforms

# FRGY

The system operates in the constant on time mode to achieve high power factor. The ON time increases with the input AC RMS voltage decreasing and the load increasing. When the operation condition is with minimum input AC RMS voltage and full load, the ON time is maximized. On the other hand, when the input voltage is at the peak value, the OFF time is maximized. Thus, the minimum switching frequency f<sub>S-MIN</sub> happens at the peak value of input voltage with minimum input AC RMS voltage and maximum load condition; Meanwhile, the maximum peak current through MOSFET and the transformer happens.

Once the minimum frequency  $f_{S-MIN}$  is set, the inductance of the transformer could be induced. The design flow is shown as below:

(a)Select N<sub>PS</sub>

$$N_{PS} \leq \frac{V_{MOS\_(BR)DS} \times 90\% - \sqrt{2}V_{AC\_MAX} - \Delta V_{S}}{V_{OUT} + V_{D\_F}} (21)$$

(b) Preset minimum frequency  $f_{S-MIN}$

(c) Compute relative  $t_s$ ,  $t_1$  ( $t_3$  is omitted to simplify the confidential design here)

$$t_{s} = \frac{1}{f_{s_{MIN}}} (22)$$

$$t_{1} = \frac{t_{s} \times N_{PS} \times (V_{OUT} + V_{D_{F}})}{\sqrt{2} V_{AC_{MIN}} + N_{PS} \times (V_{OUT} + V_{D_{F}})} (23)$$

(d) Design inductance L<sub>M</sub>

$$L_{M} = \frac{V_{AC\_MIN}^{2} \times t_{1}^{2} \times \eta}{2P_{OUT} \times t_{S}} (24)$$

(e) Compute t<sub>3</sub>

$$t_3 = \pi \times \sqrt{L_M \times C_{\text{Drain}}}$$

(25)

Where C<sub>Drain</sub> is the parasitic capacitance at drain of MOSFET

(f) Compute primary maximum peak current I<sub>P-PK-MAX</sub> and RMS current IP-RMS-MAX for the transformer fabrication.

$$I_{P\_PK\_MAX} \!=\! \frac{2P_{_{OUT}} \!\times\! [\frac{L_{_{M}}}{\sqrt{2}V_{_{AC\_MIN}}} \!+\! \frac{L_{_{M}}}{N_{_{PS}} \!\times\! (V_{_{OUT}} \!+\! V_{_{D\_F}})}]}{L_{_{M}} \!\times\! \eta}$$

$$+\frac{\sqrt{4P_{\text{OUT}}^2 \times [\frac{L_{\text{M}}}{\sqrt{2}V_{\text{AC}_{\text{MIN}}}} + \frac{L_{\text{M}}}{N_{\text{PS}} \times (V_{\text{OUT}} + V_{\text{D}_{\text{F}}})}]^2 + 4L_{\text{M}} \times \eta \times P_{\text{OUT}} \times t_3}}{L_{\text{M}} \times \eta}$$

Where  $\eta$  is the efficiency; P<sub>OUT</sub> is rated full load power

Adjust  $t_1$  and  $t_s$  to  $t_1$ ' and  $t_s$ ' considering the effect of  $t_3$

$$t'_{s} = \frac{\eta \times L_{M} \times I^{2}_{P_{P}PK\_MAX}}{4P_{OUT}} (27)$$

(26)

$$t_{1}^{\prime} = \frac{L_{M} \times I_{P\_PK\_MAX}}{\sqrt{2} V_{AC\_MIN}} (28)$$

$$I_{P\_RMS\_MAX} \approx \sqrt{\frac{t_{1}^{\prime}}{6t_{S}^{\prime}}} \times I_{P\_PK\_MAX} (29)$$

(g) Compute secondary maximum peak current I<sub>S-PK-MAX</sub> and RMS current IS-RMS-MAX for the transformer fabrication

$$I_{s_{PR},MAX} = N_{PS} \times I_{P_{PK},MAX} (30)$$

$$t_{2}' = t_{s}' - t_{1}' - t_{3} (31)$$

$$I_{s_{RMS},MAX} \approx \sqrt{\frac{t_{2}'}{6t_{s}'}} \times I_{s_{PK},MAX} (32)$$

#### Transformer design (NP,NS,NAUX)

The design of the transformer is similar with ordinary Flyback transformer. the parameters below are necessary:

| Necessary parameters          |                        |

|-------------------------------|------------------------|

| Turns ratio                   | N <sub>PS</sub>        |

| Inductance                    | L <sub>M</sub>         |

| Primary maximum current       | I <sub>P-PK-MAX</sub>  |

| Primary maximum RMS current   | I <sub>P-RMS-MAX</sub> |

| Secondary maximum RMS current | I <sub>S-RMS-MAX</sub> |

The design rules are as followed:

(a) Select the magnetic core style, identify the effective area A<sub>e</sub>

(b) Preset the maximum magnetic flux  $\Delta B$

ΔB=0.22~0.26T

<u>SY5810</u>

(c) Compute primary turn N<sub>P</sub>

$$N_{p} = \frac{L_{M} \times I_{P_{P} \times MAX}}{\Delta B \times A_{a}} (33)$$

(d) Compute secondary turn  $N_S$

$$N_{s} = \frac{N_{p}}{N_{ps}} (34)$$

(e) compute auxiliary turn N<sub>AUX</sub>

$$N_{AUX} = N_{S} \times \frac{V_{VIN}}{V_{OUT}} (35)$$

Where  $V_{VIN}$  is the working voltage of VIN pin (10V~11V is recommended).

#### (f) Select an appropriate wire diameter

With  $I_{P-RMS-MAX}$  and  $I_{S-RMS-MAX}$ , select appropriate wire to make sure the current density ranges from  $4A/mm^2$  to  $10A/mm^2$ .

(g) If the winding area of the core and bobbin is not enough, reselect the core style, go to (a) and redesign the transformer until the ideal transformer is achieved.

#### **Output capacitor Cout**

Preset the output current ripple  $\Delta I_{OUT}$ , C<sub>OUT</sub> is induced by

$$C_{\text{OUT}} = \frac{\sqrt{\left(\frac{2I_{\text{OUT}}}{\Delta I_{\text{OUT}}}\right)^2 - 1}}{4\pi f_{\text{AC}} R_{\text{LED}}} (36)$$

Where  $I_{OUT}$  is the rated output current;  $\Delta I_{OUT}$  is the demanded current ripple;  $f_{AC}$  is the input AC supply frequency;  $R_{LED}$  is the equivalent series resistor of the LED load.

## **RCD snubber for MOSFET**

The power loss of the snubber  $P_{RCD}$  is evaluated first

$$P_{\text{RCD}} = \frac{N_{\text{PS}} \times (V_{\text{OUT}} + V_{\text{D}_{-}\text{F}}) + \Delta V_{\text{S}}}{\Delta V_{\text{S}}} \times \frac{L_{\text{K}}}{L_{\text{M}}} \times P_{\text{OUT}} (37)$$

Where  $N_{PS}$  is the turns ratio of the Flyback transformer;  $V_{OUT}$  is the output voltage;  $V_{D-F}$  is the forward voltage of the power diode;  $\Delta V_S$  is the overshoot voltage clamped by RCD snubber;  $L_K$  is the leakage inductor;  $L_M$  is the inductance of the Flyback transformer;  $P_{OUT}$  is the output power.

The  $R_{RCD}$  is related with the power loss:

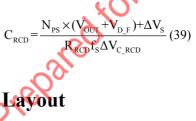

The  $C_{RCD}$  is related with the voltage ripple of the snubber  $\Delta V_{C-RCD}$ :

(a) To achieve better EMI performance and reduce line frequency ripples, the output of the bridge rectifier should be connected to the BUS line capacitor first, then to the switching circuit.

(b) The ground of the BUS line capacitor, the ground of the current sample resistor and the signal ground of the IC should be connected in a star connection.

(c) The circuit loop of all switching circuit should be kept small: primary power loop, secondary loop and auxiliary power loop.

(d) The wire connected to ISEN and DRV should be as thick as possible.

(e) The resistor divider is recommended to be put beside the IC.

264V

600V

1V.

75kHz

## **Design Example**

A design example of typical application is shown below step by step.

#1. Identify design specification

| Design Specification  |          |                  |     |

|-----------------------|----------|------------------|-----|

| V <sub>AC</sub> (RMS) | 90V~264V | V <sub>OUT</sub> | 20V |

| I <sub>OUT</sub>      | 200mA    | η                | 85% |

V<sub>D,F</sub>

f<sub>S-MIN</sub>

#2. Transformer design (N<sub>PS</sub>, L<sub>M</sub>)

Refer to Power Device Design Conditions 90V V<sub>AC,MIN</sub> V<sub>AC-MAX</sub> 50V  $\triangle V_S$ V<sub>MOS-(BR)DS</sub>

4W

100pF

(a)Compute turns ratio N<sub>PS</sub> first

$$C_{Drain} | 100pF | f_{S-MIN} | f_{S-MIN$$

$N_{PS}$  is set to

$$N_{PS}=4.2$$

$P_{\text{OUT}}$

C<sub>Drain</sub>

(**b**)f<sub>S,MIN</sub> is preset

$f_{S_{MIN}} = 75 kHz$

(c) Compute the switching period  $t_s$  and ON time  $t_1$  at the peak of input voltage.

$$t_{s} = \frac{1}{f_{s_{MIN}}} = 13.3 \mu s$$

$$t_{1} = \frac{1}{\sqrt{2}V_{AC_{MIN}} + N_{PS} \times (V_{OUT} + V_{D_{F}})}$$

$$= \frac{13.3 \mu s \times 4.2 \times (20V + 1V)}{\sqrt{2} \times 90V + 4.2 \times (20V + 1V)}$$

$$= 5.464 \mu s$$

(d) Compute the inductance  $L_M$

$$L_{M} = \frac{V_{AC\_MIN}^{2} \times t_{1}^{2} \times \eta}{2P_{OUT} \times t_{s}}$$

$$= \frac{90V^{2} \times 4.897\mu s^{2} \times 0.85}{2 \times 4W \times 13.3\mu s}$$

$$= 1.973 \text{mH}$$

Set

L<sub>M</sub>=1.6mH

(e) Compute the quasi-resonant time t<sub>3</sub>

$$t_{3} = \pi \times \sqrt{L_{M} \times C_{Drain}}$$

$$= \pi \times \sqrt{1.6 \text{mH} \times 100 \text{pF}}$$

$$= 1.257 \mu \text{s}$$

(f) Compute primary maximum peak current I<sub>P-PK-MAX</sub>

(c) Compute the quasi-resonant time

$$t_3$$

$t_3 = \pi \times \sqrt{L_M \times C_{Drain}}$

$= \pi \times \sqrt{1.6mH \times 100pF}$

$= 1.257 \mu s$

(f) Compute primary maximum peak current  $I_{P-PK-MAX}$

$I_{P_PFK_MAX} = \frac{2P_{OUT} \times \left[\frac{L_M}{\sqrt{2}V_{AC_MIN}} + \frac{L_M}{N_{PS} \times (V_{OUT} + V_{D_F})}\right]}{L_M \times \eta}$

$+ \frac{\sqrt{4P_{OUT}^2 \times \left[\frac{L_M}{\sqrt{2}V_{AC_MIN}} + \frac{L_M}{N_{PS} \times (V_{OUT} + V_{D_F})}\right]^2 + 4h_V \times \eta \times P_{OUT} \times t_3}}{L_M \times \eta}$

$= 0.39A$

Adjust switching period  $t_3$  and ON time  $t_1$  to t and  $t_1'$ .

$t_3' = \frac{\eta \times L_M \times I_{P,PK_MAX}^2}{4P_{OUT}}$

$= \frac{0.85 \times 1.6mH \times 0.39A^2}{4 \times 4W}$

$= 13.2 \mu s$

$t_1' = \frac{L_M \times I_{P,PK_MAX}}{\sqrt{2}V_{AC_MIN}}$

$= \frac{1.6mH \times 0.39A}{\sqrt{2}V_{AC_MIN}}$

Compute primary maximum RMS current IP-RMS-MAX

$$I_{P_{RMS_{MAX}}} \approx \sqrt{\frac{t'_{1}}{6t'_{s}}} \times I_{P_{PK_{MAX}}} = \sqrt{\frac{4.897\mu s}{6 \times 13.2\mu s}} \times 0.39A = 0.102A$$

(g) Compute secondary maximum peak current and the maximum RMS current.

$$I_{S_{PK_{MAX}}} = N_{PS} \times I_{P_{PK_{MAX}}} = 2.67 \times 1.038A = 2.77A$$

$\dot{t_2} = \dot{t_s} - \dot{t_1} - t_3 = 14.45 \mu s - 6.12 \mu s - 0.86 \mu s = 7.47 \mu s$

$$I_{S,RMS,MAX} \approx \sqrt{\frac{t'_2}{6t'_5}} \times I_{S_PK_MAX} = \sqrt{\frac{7.051\mu s}{6 \times 13.2\mu s}} \times 1.638A = 0.466A$$

#3. Select power MOSFET and secondary power diode

Refer to Power Device Design

| Known condition                                                   | ns at this step                                                                                                               |                                 |        |

|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------|

| V <sub>AC-MAX</sub>                                               | 264V                                                                                                                          | N <sub>PS</sub>                 | 4.2    |

| V <sub>OUT</sub>                                                  | 20V                                                                                                                           | V <sub>D-F</sub>                | 1V     |

| $\Delta V_{S}$                                                    | 50V                                                                                                                           | η                               | 85%    |

| $V_{MOS_{DS}_{MAX}} = \sqrt{2}$                                   | voltage and the current s<br>$V_{AC\_MAX} + N_{PS} \times (V_{OUT} + V_{I})$<br>$\times 264V + 4.2 \times (20V + 1V)$<br>1.5V | $_{_{\rm F}})+\Delta V_{\rm S}$ | sbaren |

| $I_{MOS_{PK_{MAX}}} = I_{P_{P}PP}$                                | <sub>C_MAX</sub> =0.39A                                                                                                       | tian                            |        |

| $I_{MOS_{RMS}_{MAX}} = I_{P_{P_{P_{P_{P_{P_{P_{P_{P_{P_{P_{P_{P_$ | <sub>RMS_MAX</sub> =0.102A                                                                                                    | eiden.                          |        |

| $(\mathbf{h})$ Comments the                                       | 14                                                                                                                            |                                 | C.J.   |

$$V_{MOS_{DS}_{MAX}} = \sqrt{2} V_{AC_{MAX}} + N_{PS} \times (V_{OUT} + V_{D_{F}}) + \Delta V_{S}$$

=  $\sqrt{2} \times 264V + 4.2 \times (20V + 1V) + 50V$

= 511.5V

(b) Compute the voltage and the current stress of secondary power diode

$$V_{D_{PR}MAX} = \frac{\sqrt{2}V_{AC_MAX}}{N_{PS}} + V_{OUT}$$

=  $\frac{\sqrt{2} \times 264V}{4.2} + 20V$

= 108.9V

$I_{D_{PK}MAX} = N_{PS} \times I_{P,PK_MAX} = 4.2 \times 0.39 \text{ A} = 1.638 \text{ A}$

$I_{D_{AVG}} = I_{OUT} = 0.32 \text{ A}$

#4. Select the output capacitor C<sub>OUT</sub>

Refer to Power Device Design

# SY5810

| Conditions       |       |                  |                     |

|------------------|-------|------------------|---------------------|

| I <sub>OUT</sub> | 200mA | $\Delta I_{OUT}$ | 0.3I <sub>OUT</sub> |

| f <sub>AC</sub>  | 50Hz  | R <sub>LED</sub> | 6×1.6Ω              |

The output capacitor is

| $C_{OUT} = \frac{\sqrt{\left(\frac{2I_{OUT}}{\Delta I_{OUT}}\right)^2}}{4\pi f_{AC}R_{LED}}$ | -<br>1<br>-                                                                                                                     |      |                       |     |       |    |

|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------|-----------------------|-----|-------|----|

| $=\frac{\sqrt{(\frac{2\times0.24}{0.6\times0.2}}}{4\pi\times50\text{Hz}\times}$              | $\frac{A}{2A}$ ) <sup>2</sup> -1                                                                                                |      |                       |     | dior  | 40 |

| =527µF                                                                                       |                                                                                                                                 |      |                       |     | s.    |    |

| #5. Design RCD sn                                                                            | ubber                                                                                                                           |      |                       |     | · 40' |    |

| Refer to Power Dev                                                                           | rice Design                                                                                                                     |      |                       | 19  | ò.    |    |

| Conditions                                                                                   |                                                                                                                                 |      |                       | 2   |       |    |

| V <sub>OUT</sub>                                                                             | 20V                                                                                                                             |      | $\Delta V_{S}$        |     | 50V   |    |

| N <sub>PS</sub>                                                                              | 4.2                                                                                                                             | ]    | $L_{\rm K}/L_{\rm M}$ | S V | 1%    |    |

| P <sub>OUT</sub>                                                                             | 4W                                                                                                                              |      |                       | •   |       |    |

| The power loss of t                                                                          |                                                                                                                                 | Pour | ilali                 |     |       |    |

| $P_{\rm RCD} = \frac{N_{\rm PS} \times (V_{\rm OUT} + \Delta V)}{\Delta V}$                  | $\frac{V_{D_F}}{V_s} \times \frac{L_K}{L_M} \times F$                                                                           | Pout |                       |     |       |    |

| $=\frac{4.2\times(20\mathrm{V}+1)}{50\mathrm{V}}$                                            | $\frac{V_{D_F}) + \Delta V_S}{V_S} \times \frac{L_K}{L_M} \times F$                                                             | K    |                       |     |       |    |

| =0.111W                                                                                      | C                                                                                                                               |      |                       |     |       |    |

| The resistor of the s                                                                        | snubber is                                                                                                                      |      |                       |     |       |    |

| $R_{RCD} = \frac{(N_{PS} \times (V_{OUT}))}{1}$ $= \frac{(4.2 \times (20))}{9.1}$            | $+V_{D_{s}}+\Delta V_{s})^{2}$                                                                                                  |      |                       |     |       |    |

| $=\frac{(4.2\times(20))}{0.11}$                                                              | $\frac{1V}{1W}$                                                                                                                 |      |                       |     |       |    |

| $=176k\Omega^{\circ}$                                                                        |                                                                                                                                 |      |                       |     |       |    |

| The capacitor of the $N_{\rm eff}$                                                           |                                                                                                                                 |      |                       |     |       |    |

| $C_{\rm RCD} = \frac{N_{\rm PS} \times (V_{\rm OUT})}{R_{\rm RCD} f_{\rm S} \ell}$           | $\frac{(\mathbf{v}_{\mathrm{D}_{\mathrm{F}}}) + \Delta \mathbf{v}_{\mathrm{S}}}{\Delta \mathbf{V}_{\mathrm{C}_{\mathrm{RCD}}}}$ |      |                       |     |       |    |

| = 4.2×(20V+                                                                                  | ·1V)+50V                                                                                                                        |      |                       |     |       |    |

| $178k\Omega \times 100$                                                                      | kHz×25V                                                                                                                         |      |                       |     |       |    |

| =0.3nF                                                                                       |                                                                                                                                 |      |                       |     |       |    |

#6. Set VIN pin

Refer to Start up

| Conditions           |                |                      |                          |

|----------------------|----------------|----------------------|--------------------------|

| V <sub>BUS-MIN</sub> | 90V×1.414      | V <sub>BUS-MAX</sub> | 264V×1.414               |

| I <sub>ST</sub>      | 15µA (typical) | V <sub>IN-ON</sub>   | 16V (typical)            |

| I <sub>VIN-OVP</sub> | 2mA (typical)  | t <sub>ST</sub>      | 500ms (designed by user) |

(a) R<sub>ST</sub> is preset

| Parameters designed |      |                      |       |

|---------------------|------|----------------------|-------|

| R <sub>COMP</sub>   | 500Ω | V <sub>COMP,IC</sub> | 450mV |

| C <sub>COMP1</sub>  | 2μF  | C <sub>COMP2</sub>   | 100pF |

ort

#8 Set current sense resistor to achieve ideal output current

#### Refer to Primary-side constant-current control

| Known conditions at this step |      |                  |      |  |  |  |

|-------------------------------|------|------------------|------|--|--|--|

| $k_1 \times k_2$              | 0.16 | N <sub>PS</sub>  | 4.2  |  |  |  |

| V <sub>REF</sub>              | 0.3V | I <sub>OUT</sub> | 0.2A |  |  |  |

The current sense resistor is

$$R_{s} = \frac{k_{1} \times k_{2} \times V_{REF} \times N_{PS}}{I_{OUT}}$$

$$= \frac{0.16 \times 0.3V \times 4.2}{0.2A}$$

$$= 1.008\Omega$$

#9 set ZCS pin

# Refer to Line regulation modification and Over Voltage Protection (OVP) Open Loop Protection (OLP)

First identify R<sub>ZCSU</sub> need for line regulation.

| Known conditio    | ns at this step |  |  |

|-------------------|-----------------|--|--|

| k <sub>3</sub>    | 68              |  |  |

| Parameters Desi   | igned           |  |  |

| R <sub>ZCSU</sub> | 200kΩ           |  |  |

|                   |                 |  |  |

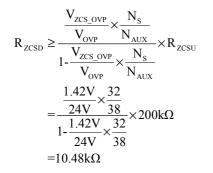

| Then compute R <sub>ZCSD</sub> |          | ON I             |     |

|--------------------------------|----------|------------------|-----|

| Conditions                     |          | $\mathbf{v}$     |     |

| V <sub>ZCS OVP</sub>           | 1.42V    | V <sub>OVP</sub> | 48V |

| V <sub>OUT</sub>               | 20V      |                  |     |

| Parameters designed            | <u> </u> |                  |     |

| R <sub>ZCSU</sub>              | 100kΩ    |                  |     |

| N <sub>S</sub>                 | 32       | N <sub>AUX</sub> | 38  |

|                                |          |                  | •   |

$R_{zCSD} < \frac{\frac{V_{ZCS_OVP}}{V_{OUT}} \times N_{AUX}}{1 - \frac{V_{ZCS_OVP}}{V_{OUT}} \times \frac{N_S}{N_{AUX}}} \times R_{zCSU}$   $= \frac{1.42V}{20V} \times \frac{32}{38} \times 200 \text{k}\Omega$   $= 12.7 \text{k}\Omega$

$R_{ZCSD}$  is set to

$R_{ZCSD} = 11.05 k\Omega$

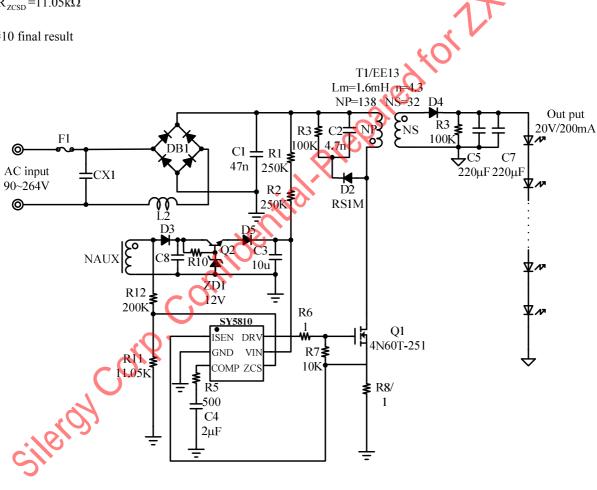

#10 final result

# www.s-manuals.com